面向火控計算機的端口與接口集成電路設計服務

在現代國防與航空航天系統中,火控計算機扮演著核心決策與數據處理單元的角色。其性能、可靠性與實時性直接關系到整個武器系統的效能。作為連接火控計算機與外部傳感器(如雷達、光電探測器)、執行機構(如伺服系統)及上級指揮網絡的橋梁,端口電路與接口電路的設計至關重要。專業的集成電路(IC)設計服務,能夠為此類高要求應用提供定制化、高性能、高可靠的解決方案。

一、 核心需求分析與設計挑戰

火控計算機接口電路設計并非標準通用設計,其面臨一系列獨特挑戰:

- 極高的實時性:從傳感器數據采集到火控解算,再到指令下發,必須在極短的時間內完成,要求接口電路具有極低的延遲和確定性的時序。

- 極端環境適應性:需在寬溫范圍、強振動、電磁干擾復雜的惡劣環境下穩定工作,對電路的抗干擾能力、散熱設計和可靠性提出了軍品甚至宇航級的要求。

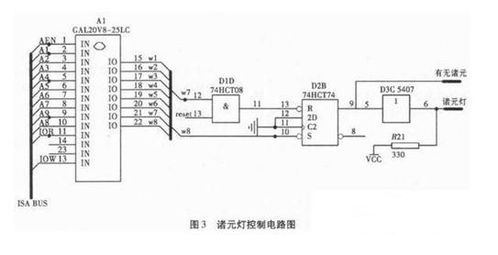

- 多協議異構集成:需要同時處理高速串行數據(如光纖通道、SerDes)、標準總線(如1553B、ARINC 429、CAN總線)及專用模擬/數字I/O信號,電路需具備強大的協議轉換與數據整合能力。

- 高安全性與保密性:數據傳輸需考慮加密、認證和防篡改機制,從硬件層面筑牢安全屏障。

- 小型化與低功耗:平臺空間和能源有限,要求電路高度集成,在滿足性能的同時優化功耗。

二、 端口與接口IC設計服務的關鍵技術環節

專業的IC設計服務將圍繞以下核心環節展開:

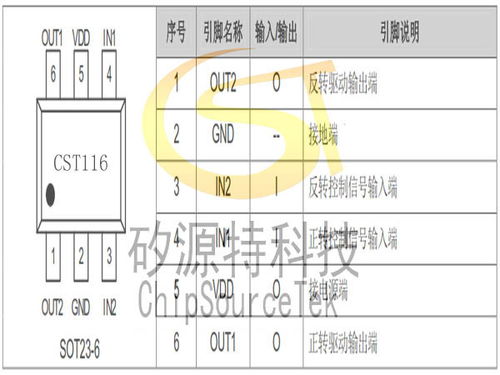

- 架構定義與規格制定:與客戶深度溝通,明確所有接口類型、數據速率、電氣標準(如LVDS、PECL)、協議棧、時序預算、功耗預算及環境等級要求,形成精確的設計規格書。

- 混合信號電路設計:

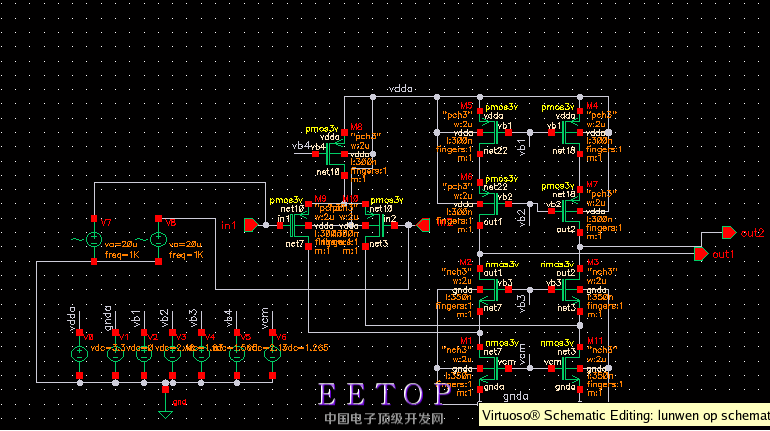

- 高速數字端口:設計用于高速串行通信的物理層(PHY),包括時鐘數據恢復(CDR)、串并/并串轉換(SERDES)、預加重/均衡等電路,以保障信號完整性。

- 專用模擬接口:設計用于直接連接傳感器的前端電路,如高精度ADC/DAC驅動、采樣保持、可編程增益放大及濾波電路。

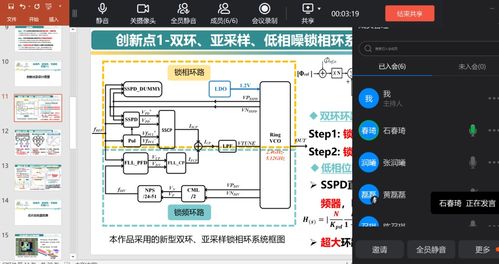

- 電源與時鐘管理:設計低噪聲、高效率的片上電源調節模塊(LDO/DCDC)及高穩定性、低抖動的時鐘生成與分發網絡(PLL)。

- 數字邏輯與協議處理集成:

- 使用硬件描述語言(如Verilog/VHDL)設計協議控制器(如1553B BC/RT/MT終端、ARINC 429編解碼器)、數據緩沖FIFO、DMA控制器及與主處理器(如PowerPC、ARM)的本地總線接口(如AXI、AHB)。

- 集成硬件加速單元,用于特定的加密算法(如AES、SHA)或數據處理任務,以減輕CPU負擔。

- 可靠性設計與驗證:

- 輻射加固設計:針對空間應用,采用特殊的電路設計(如DICE鎖存器)、版圖技術及工藝選擇,抗單粒子效應(SEE)和總劑量效應(TID)。

- 全定制版圖設計:進行精密的物理設計,優化信號走線、電源網格、ESD保護和抗 latch-up 結構,以滿足嚴格的電氣和可靠性標準。

- 全面仿真與驗證:進行前端功能仿真、后端時序驗證、信號完整性/電源完整性(SI/PI)分析,以及針對溫度、工藝角(PVT)的蒙特卡洛分析,確保設計在極端條件下仍能正常工作。

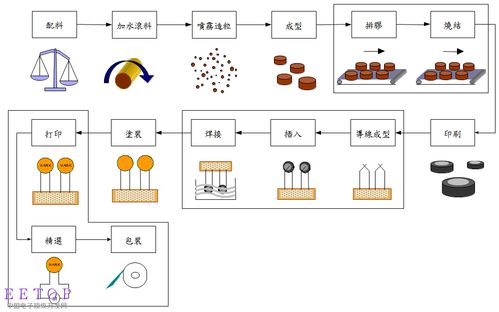

- 測試與封裝:制定詳盡的測試方案,設計測試向量,并選擇適合的封裝形式(如陶瓷BGA、QFN),確保芯片可測試、可生產并滿足機械與熱學要求。

三、 服務價值與交付成果

通過專業的IC設計服務,客戶可以獲得:

- 定制化芯片(ASIC)或現場可編程門陣列(FPGA)配置代碼:一個高度集成、針對火控應用優化的專用接口芯片或IP核。

- 顯著的系統優勢:

- 性能提升:硬件實現的協議處理和高速接口,遠超軟件方案的速度。

- 可靠性增強:減少外部分立元件數量,從源頭提升系統MTBF(平均無故障時間)。

- 安全性內嵌:硬件級的安全模塊更難被攻擊和篡改。

- 體積與功耗優化:高集成度大幅縮小板卡面積,降低整體功耗。

- 完整的技術文檔:包括設計規范、驗證報告、芯片手冊、應用筆記等。

- 持續的技術支持:協助客戶完成芯片評估、系統集成和后續迭代。

為火控計算機設計端口與接口電路,是一項涉及多學科深度交叉的復雜工程。依托專業的集成電路設計服務,可以將系統級的苛刻要求,轉化為硅片層面的精巧實現,從而為下一代高性能、高可靠的火控系統奠定堅實的硬件基礎。這不僅是一項技術服務,更是提升國防裝備核心競爭力的關鍵戰略投資。

如若轉載,請注明出處:http://www.021zx.cn/product/68.html

更新時間:2026-02-23 01:40:30