憶往昔 從集成門控時鐘到分離門控,淺談IC設計EDA虛擬機服務器的搭建與服務演進

在當今高度復雜的集成電路設計領域,效率與精度是決定成敗的關鍵。隨著工藝節點不斷微縮,設計規模呈指數級增長,傳統的本地工作站模式已難以應對海量數據處理、協同設計與版本管理的挑戰。因此,搭建一個穩定、高效、可擴展的IC設計EDA(電子設計自動化)虛擬機服務器集群,已成為眾多設計公司與研究機構的必然選擇。這不僅是一個技術基礎設施的構建,更承載著設計方法與服務模式的深刻演進。

EDA虛擬機服務器:現代IC設計的數字基石

搭建一個專業的EDA虛擬機服務器環境,遠非簡單地將軟件安裝到幾臺虛擬機上。它需要一個精心設計的架構,通常包括:

- 計算資源池:由高性能CPU(通常支持多核多線程)和GPU(用于加速仿真與驗證)組成的服務器集群,通過虛擬化技術(如VMware, KVM)靈活分配資源。

- 集中存儲系統:采用高速網絡(如InfiniBand)連接的NAS或SAN,確保所有設計數據、庫文件、工藝文檔的單一可信源,實現團隊間無縫共享與版本控制。

- 許可與作業調度:集成專業的許可管理(如FlexNet)和作業調度系統(如LSF, SLURM),公平、高效地分配昂貴的EDA工具許可,并管理大批量的仿真、綜合、物理實現作業。

- 網絡與安全:高帶寬、低延遲的內部網絡,以及嚴格的防火墻、訪問控制和數據加密策略,保護核心知識產權。

- 自動化部署與運維:利用容器化(如Docker)和配置管理工具,實現EDA工具環境與設計流程的快速部署、復制與恢復,提升運維效率。

這樣的環境使得工程師可以隨時隨地通過終端訪問統一的設計平臺,大幅提升了協作效率,縮短了設計周期。

時鐘技術的演進:從“集成”到“分離”的設計哲學

在搭建的服務器上運行的設計流程中,低功耗設計始終是核心挑戰之一,而時鐘網絡是其中的功耗大戶。這不禁讓我們“憶往昔”,回顧時鐘門控技術的關鍵演進。

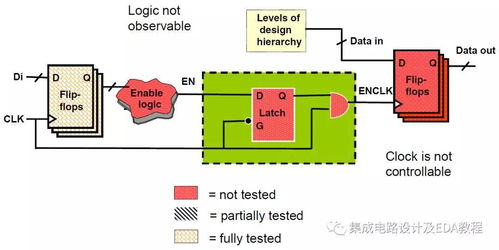

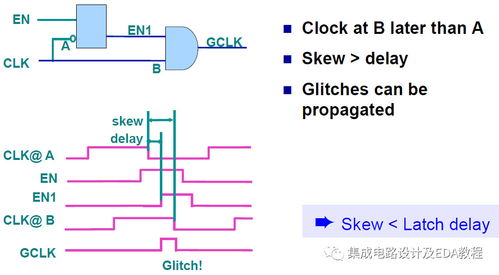

- 集成門控時鐘技術的前世:在早期或較簡單的設計中,時鐘門控邏輯往往與功能邏輯緊密耦合、分散設計。即,在寄存器或模塊層級,由組合邏輯直接產生門控使能信號來控制本地時鐘的開關。這種方法直觀,但缺乏全局視野,容易導致時鐘偏移(Skew)控制困難、門控效率不均衡,且在整個設計中進行功耗分析和優化較為繁瑣。它反映了當時以功能實現為首要,功耗優化為次要附加的設計思路。

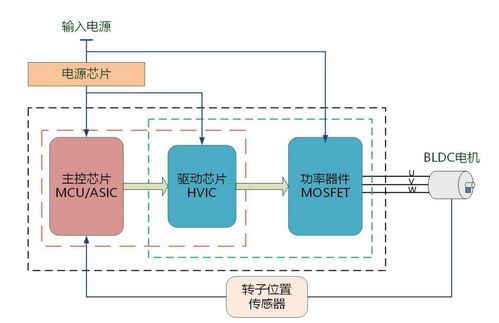

- 分離門控時鐘技術的今生:隨著工藝進步和功耗要求日益嚴苛,特別是多電壓域、動態電壓頻率調節(DVFS)等技術的應用,分離的、結構化的時鐘門控技術成為主流。其核心思想是將時鐘控制邏輯(時鐘門控單元,ICG)作為標準單元庫的一部分,在物理實現階段由工具(如邏輯綜合、布局布線工具)根據活動性分析,自動、有規劃地插入到時鐘樹中。這種方法將“功能”與“時鐘管理”分離,允許后端工具構建一個功耗更優、時序更穩健的時鐘樹網絡。它體現了現代IC設計高度自動化、關注可制造性與可靠性的系統級設計哲學。

集成電路設計服務:云化與專業化未來

EDA虛擬機服務器環境的成熟,正推動著集成電路設計服務模式向更深層次發展。

- 設計環境即服務(DEaaS):服務商可以提供預配置、可立即投入使用的完整EDA云端環境,客戶無需自建基礎設施,按需訂閱即可獲得從架構探索到版圖交付的全流程工具支持。

- 專業化與垂直整合:設計服務不再僅僅是人力外包,而是結合特定領域知識(如AI加速器、射頻、汽車電子)和內部優化的IP、方法學與自動化腳本,提供“芯片設計解決方案”。服務器集群成為承載這些專有技術和流程的平臺。

- 協同設計與安全沙箱:基于云端的服務器環境,便于Fab、IP供應商、設計公司與終端客戶在受控的安全“沙箱”內進行數據共享和協同調試,加速問題定位與解決。

- 大數據與AI驅動設計:集中的服務器環境積累了海量設計過程數據(時序、功耗、面積日志),為應用機器學習算法進行設計預測、自動優化和良率提升提供了可能。

###

從手動分散的時鐘門控到工具自動化的分離式時鐘樹綜合,從孤島式的設計工作站到集中化的EDA虛擬機服務器集群,集成電路設計的歷程是一部不斷追求抽象層次提升、自動化程度加強和協作范圍擴大的歷史。今天,我們搭建的不僅僅是一個服務器,更是一個支撐創新、融合技術與服務、面向未來“硅基”產品創造的數字樞紐。在這個樞紐上,昔日的設計智慧與明天的智能算法交匯,共同繪制著下一代芯片的藍圖。

如若轉載,請注明出處:http://www.021zx.cn/product/50.html

更新時間:2026-02-23 19:05:23